1 Feldeffekttransistoren Feldeffekt bezeichnet die Einwirkung eines elektrischen Feldes auf elektrische Ladungsträger. Diesen Effekt nutzen alle Feldeffekttransistoren. Dabei verwenden sie im Gegensatz zu bipolaren Transistoren lediglich Ladungsträger einer Art, weshalb sie auch als unipolare Transistoren bezeichnet werden. Der größte Vorteil der Feldeffekttransistoren ist ihre Fähigkeit Ströme leistungslos und somit für den Nutzer ungefährlicher zu steuern. 1.1 Sperrschicht-Feldeffekttransistoren  1.1.1Aufbau 1.1.1Aufbau

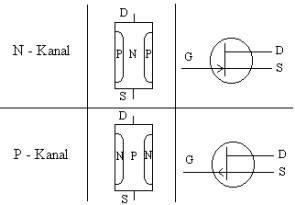

Sperrschicht-Feldeffekttransistoren bestehen aus einem dünnen P- oder N-dotiertem Kristallplättchen, dem so genannten Kanal. An den Kanal sind die beiden Elektroden Drain (D) und Source (S) angebracht. Um einen Einfluß auf die Wirkungsweise des FETs zu bekommen, sind seitlich um den Kanal zwei andersartig dotierte Flächen aufgebracht (Bild 1). Diese Schichten sind miteinander verbunden und es ist das Gate (G), die Steuerelektrode, an ihnen angebracht. So entstehen zwischen dem Kanal und dem Gate zwei PN-Übergänge, die den Kanal in seiner Breite begrenzen.

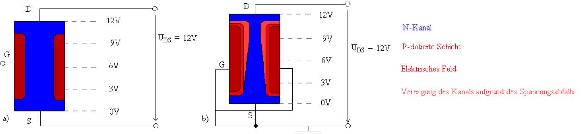

Bild 1 1.1.2 Wirkungsweise 1.1.2.1 N-Kanal JFET Wie bereits erwähnt wird der N-Kanal in seiner Breite durch die seitlichen PN-Übergänge begrenzt.Wird an den N-Kanal J-FET eine Spannung vom Drain zur Source angelegt, so verhält sich der Kanal wie ein ohmscher Widerstand und die angelegte Spannung fällt längs der Strecke des Kanals ab (Bild 2a).

Bild 2

Legt man jedoch das Gate zusätzlich mit Source auf Masse, so werden die PN-Übergänge in Sperrichtung betrieben. An den Grenzflächen bildet sich eine Sperrschicht aus. Die im P-dotiertem Material vorhandenen Defektelektronen werden von der negativen Spannung am Gate angezogen und dieser Bereich verarmt an Ladungsträgern. So bildet sich ein negatives, elektrisches Feld, welches die Elektronen beim Durchfließen des Kanals behindert (Bild 2b, Bild 3). Die Spannung am Gate (U GS ) muß immer negativ sein und darf 0V damit nicht überschreiten, da die PN-Übergänge sonst in Durchlassrichtung betrieben werden würden, was einen Strom Legt man jedoch das Gate zusätzlich mit Source auf Masse, so werden die PN-Übergänge in Sperrichtung betrieben. An den Grenzflächen bildet sich eine Sperrschicht aus. Die im P-dotiertem Material vorhandenen Defektelektronen werden von der negativen Spannung am Gate angezogen und dieser Bereich verarmt an Ladungsträgern. So bildet sich ein negatives, elektrisches Feld, welches die Elektronen beim Durchfließen des Kanals behindert (Bild 2b, Bild 3). Die Spannung am Gate (U GS ) muß immer negativ sein und darf 0V damit nicht überschreiten, da die PN-Übergänge sonst in Durchlassrichtung betrieben werden würden, was einen Strom

Bild 3

zwischen Gate und Source zurFolge hätte. Das würde wiederum bedeuten das der Strom durch den Kanal (I D ) nicht leistungslos gesteuert werden würde, was beim J-FET ja der Sinn ist. Der Kanal wird in der Nähe des Drain-Anschlusses mehr eingeschränkt als im der Nähe der Source, dies lässt sich durch den Spannungsabfall über die Strecke des Kanals begründen. Da das Gate und der Minuspol der Spannung U DS gemeinsam auf Masse liegen, liegt zwischen dem ersten Punkt des Kanals (Bild 2b) und dem Gate ein Potential von 12V, während Bild 3 im dritten Punkt nur noch eine Spannung von ca. 6V auf die Sperrschicht wirkt. Der Einfluß der größeren Spannung im ersten Punkt ruft eine größere Sperrschicht hervor als dies im dritten Punkt der Fall ist. 1.1.2.2 P-Kanal JFET: (Bild 4)  Es ist auch möglich einen JFET als P-Kanal zu realisieren, dessen Leitfähigkeit jedoch im Gegensatz zum N-Kanal JFET durch eine positive Spannung am Gate eingeschränkt werden kann; während die Spannung zwischen Drain und Source negativ zu Wählen ist. Es ist auch möglich einen JFET als P-Kanal zu realisieren, dessen Leitfähigkeit jedoch im Gegensatz zum N-Kanal JFET durch eine positive Spannung am Gate eingeschränkt werden kann; während die Spannung zwischen Drain und Source negativ zu Wählen ist.

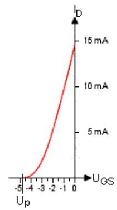

Im P-Kanal fließt ein Strom, der durch Störstellenleitung verursacht wird. Es sind also Defektelektronen, die einen Stromfluß im Kanal hervorrufen (Bild 4). Legt man nun an das Gate eine Positive Spannung an, so werden wieder zuerst die freien Ladungsträger (Elektronen) aus den den Kanal umgebenden Zonen (hier N-Zonen) „abgesogen“. Das Positive, elektrische Feld an den Sperrschichten verdrängt die Defechtelektronen und beschränkt den Kanal in seiner Breite, was einen Abfall von I D zur Folge hat. 1.1.3 Kennlinien 1.1.3.1 Steuerkennlinie (Bild 5)  Die folgenden Angaben beziehen sich auf N-Kanal JFETs, sie können aber unter der Voraussetzung, dass die umgekehrte Pohlung der Spannung und des Stromes beachtet wird, auf den P-Kanal FETs übertragen werden. Die folgenden Angaben beziehen sich auf N-Kanal JFETs, sie können aber unter der Voraussetzung, dass die umgekehrte Pohlung der Spannung und des Stromes beachtet wird, auf den P-Kanal FETs übertragen werden.

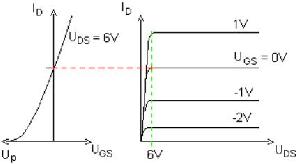

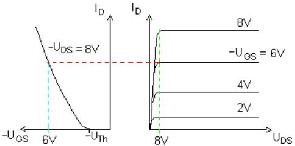

Bild 5 zeigt die sogenannte Steuerkennlinie (Eingangskennlinie) eines N-Kanal JFETs. Diese beschreibt die Abhängigkeit des Drainstromes I D von der Gate-Source-Spannung U GS. Um die Kennlinie mittels einer geeigneten Messschaltung aufnehmen zu können, ist die Drain-Source-Spannung konstant zu halten, wobei die Spannung -U GS von Null ausgehend gesteigert wird. Es ist zu erkennen, dass der kleinste Wert von -U GS den größten Drainstrom verursacht, was darauf zurück zu führen ist dass die kleinste negative Spannung am Gate auch die kleine Sperrschicht an den PN-Übergängen des FETs hervorruft und der Kanal somit am wenigsten eingeschränkt wird. Erhöht man die Spannung weiter, so verringert sich auch der Strom immer weiter bis er bei der sogenannten Abschnürrspannung U p vollständig auf Null abgesunken ist. Zusätzlich lässt sich aus der Steuerkennlinie des N-Kanal JFETs die Steilheit S ablesen, sie ist ein wichtiger Kennwert des FETs und ein Faktor bei der Brechung der Verstärkung.

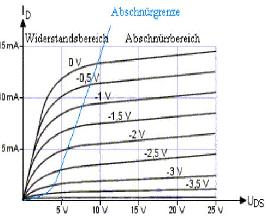

1.1.3.2 Ausgangskennlinienfeld (Bild 6)  Bild 6 zeigt das Ausgangskennlinenfeld eines N-Kanal JFETs dar, welche die Abhängigkeit des Drainstroms I D von der Drain-Source-Spannung U DS. Bei der Aufnahme der einzelnen Kennlinien muss darauf geachtet werden, dass die Spannung –U GS einen konstanten Wert hat, da sich für jede Gate-Source-Spannung eine andere Kennlinie ergibt. Bei einer Spannung von U GS = 0V ist der Kanal am breitesten, bamit fließt bei dieser Spannung der größtmögliche Drain-Strom I D . Überträgt man die Werte der einzelnen Kennlinien in ein anderes Diagramm, so kann die Steuerkennlinie aus den Ausgangskennlinien ermittelt werden. Bild 6 zeigt das Ausgangskennlinenfeld eines N-Kanal JFETs dar, welche die Abhängigkeit des Drainstroms I D von der Drain-Source-Spannung U DS. Bei der Aufnahme der einzelnen Kennlinien muss darauf geachtet werden, dass die Spannung –U GS einen konstanten Wert hat, da sich für jede Gate-Source-Spannung eine andere Kennlinie ergibt. Bei einer Spannung von U GS = 0V ist der Kanal am breitesten, bamit fließt bei dieser Spannung der größtmögliche Drain-Strom I D . Überträgt man die Werte der einzelnen Kennlinien in ein anderes Diagramm, so kann die Steuerkennlinie aus den Ausgangskennlinien ermittelt werden.

Man unterscheidet im Ausgangskennlinienfeld zwei Bereiche, die durch die Abschnürgrenze von einander getrennt sind. Links von der Abschnürgrenze befindet sich derWiderstandsbereich, in dem sich der Drainstrom nahezu nach dem ohmschen Gesetz vergrößert. Im Abschnürrbereich hingegen verursacht eine Erhöhung von U DS einen größeren Spannunggsabfall über die Strecke des N-Kanals und damit eine Vergrößerung der Sperrschichten; der Kanal ist jetzt völlig abgeschnürt. Der Strom I D würde sich durch eine weitere Erhöhung von U DS aber selbst abschnüren, da ein weiteres Ansteigen des Stroms die Sperrschichten mehr zusammendrückt. Und ein Sinken von I D verursacht wiederum eine Verkleinerung der Sperrschichten was zur Folge hat das der Drainstrom wieder steigt. Deshalb bleibt der Strom im Abschnürbereich nahezu konstant.

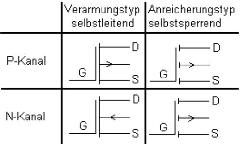

1.2 Isolierschicht-Feldefekttransistoren (MOS-FET) Bild 8  Neben den Sperrschicht-FETs gibt es noch eine zweite Variante der Feldeffekttransistoren, die Isolierschicht-FETs. Neben den Sperrschicht-FETs gibt es noch eine zweite Variante der Feldeffekttransistoren, die Isolierschicht-FETs.

Der Unterschied zum Sperrschicht Feldeffekttransistor ist der Umstand, dass das Gate durch eine Isolierschicht vom Substrat getrennt ist. Diese Isolierschicht besteht aus Siliziumdioxid und ist sehr dünn (< 0,1µm).

Bei den Isolierschicht Feldeffekttransistoren unterscheidet man zwei Typen, den Verarmung- und den Anreicherungstyp (Bild 8). 1.2.1 Selbstleitende MOS-FET

<>

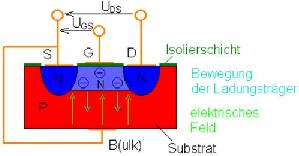

Die Darstellung in Bild 9 zeigt den Querschnitt eines N-Kanal MOS-FETs, mit einem P-dotierten Substrat, an dass der Anschluss des Bulks angebracht ist, welches eine Verbindung mit dem Source Anschluss hat. Die Anschlüsse von Drain und Source sind in zwei N-Zonen eingebracht. Wie zu erkennen ist, ist zwischen den Anschlüssen von Source und Drain eine schwach dotierte N-Zone eingelassen. Wird eine Spannung zwischen die Anschlüsse Drain und Source angelegt, so fließt durch den bereits vorhandenen N-Kanal ein Strom I D, ohne das eine Spannung an der Steuerelektrode Gate anliegt. Diesen Effekt bezeichnet man als selbstleitend. Betrachtet man die Eingangskennline neben dem Ausgangskennlinienfeld (Bild 10); so erkennt man dass die Ausgangskennlinie genau an dem Wert die Achse des Drainstroms schneidet, zu dem die Gate-Source-Spannung U GS = 0V beträgt. Legt man zusätzlich an das Gate eine negative Spannung an, so werden die Ladungsträger innerhalb des N-Kanals durch das elektrische Feld aus dem Kanal gedrängt, wodurch die Leitfähigkeit des MOS-FETs nachlässt. Da der Kanal hier an Ladungsträgern verarmt, werden selbstleitende MOS-FETs auch als Verarmungtypen bezeichnet. Bei einer positiven Spannung am Gate nimmt die Leitfähigkeit des Kanals zu. Bei der Erstellung eines selbstleitenden P-Kanal MOS-FET muss darauf geachtet werden, dass sowohl die Dotierung der Schichten als auch die Polung der Spannungen umzukehren ist. 1.2.2 selbstsperrende MOS-FET

<>

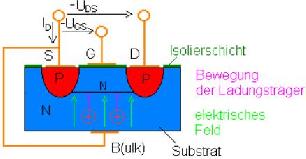

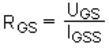

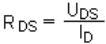

Der in Bild 11 dargestellte P-Kanal MOS-FET ist als ein N-dotiertes Substrat realisiert, in das zwei P-dotierte Zonen eingelassen wurden, auf die die Anschlüsse des Drains und der Source aufgebracht sind. Auch hier ist die Source durch den Bulkanschulss mit dem Substrat verbungen. Wie bereits erwähnt werden für P-Kanal MOS-FETs die umgekerten Polungen verwendet. Bei einer Spannung –U DS = 0V kann kein Strom zwischen Source und Drain fließen, da die P-Zonen durch das negativ dotierte Substrat von einander getrennt sind, weshalb von einem selbstsperrenden MOS-FET die rede ist. Betrachtet man die Steuerkennlinie (Bild 12 links), so erkennt man, dass bei konstantem -U DS eine Erhöhung von –U GS keinen Drainstrom verursacht; bis zum erreichen der Schwellen-Spannung –U Th . Wird diese überschritten so steigt der Drainstrom nahezu proportional zur Gatespannung. Dies begründet sich darin, dass durch das Anlegen der Spannung –U GS ein elektrisches Feld vom Bulk zum Gate entsteht. Dieses Feld drückt freie im Substrat enthaltene Defecktelektronen in den Kanal. Der P-Kanal des FETs wird mit Ladungsträgern angereichert, weshalb er auch als Anreicherungstyp bezeichnet wird. Ein Stromfluß von der Source nach Drain ist jetzt möglich. Die Stärke des Drainstromes lässt sich durch variieren von –U GS verändern. Zur Herstellung eines N-Kanal selbstsperrenden MOS-FETs werden die Schichten umgekehrt dotiert. Es ist genauso die Umgekehrte Polung der Spannungen zu verwenden. 1.1.4 Kenn- und Grenzdaten Name | Bezeichnung | Erläuterung | Formel | U GS | Gate Spannung | Spannung zwischen Gate und Source (Eingangsspannung) | | U DS | Dain-Source-Spannung | Ausgangsspannung | | I D | Drainstrom | Strom zwischen Drain und Source | | U p | Abschnürrspannung Pinch off – voltage | Spannungswert von U GS , bei dem der Kanal völlig abgeschnürt ist | | U Th | Thresehold- / Schwell-Spannung | Schwellwert, ab dem der Kanal eines selbstsperrenden MOS-FETs von ladungsträgern überflutet wird | | I GSS | Reststrom | Durch Eigenleitung bedingter Strom zwischen Gate und Source | | R GS | Eingangswiderstand | Widerstand zwischen Gate und Source. Da I GSS fast 0A beträgt ist der dynamische Eingangswiderstand nahezu unendlich |

| R DS | Statischer Ausgangswiderstand | Widerstand von Drain nach Source, in einem bestimmten Arbeitspunkt |

| r DS | Dynamischer/ differenzieller Ausgangswiderstand | Ausgangswiderstand bei Wechselspannungen |

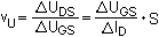

| S | Steilheit | Steigung der Eingangskennlinie |

| v U | Spannungsverstärkung | Verstärkung der Eingangsspannung |

| Quellen Verlag | Autor | Titel | Stam | Finke, Frielingsdorf, Litermann, Schaefer | Kommunikationstechnik | Vogel | Klaus Beuth | Bauelemente | Handwerk und Technik | | Elektronik für Berufsschulen | Expert Verlag Frech-Verlag | Adolf Rötzel | Halbleiter-Bauelemente | Druckansicht

Feldeffekttransistoren

|